Non ci sono prodotti a carrello.

Il chip di test fabbricato con il processo TSMC da 7nm raggiunge una velocità di trasferimento dati pari a 4400MT/s.

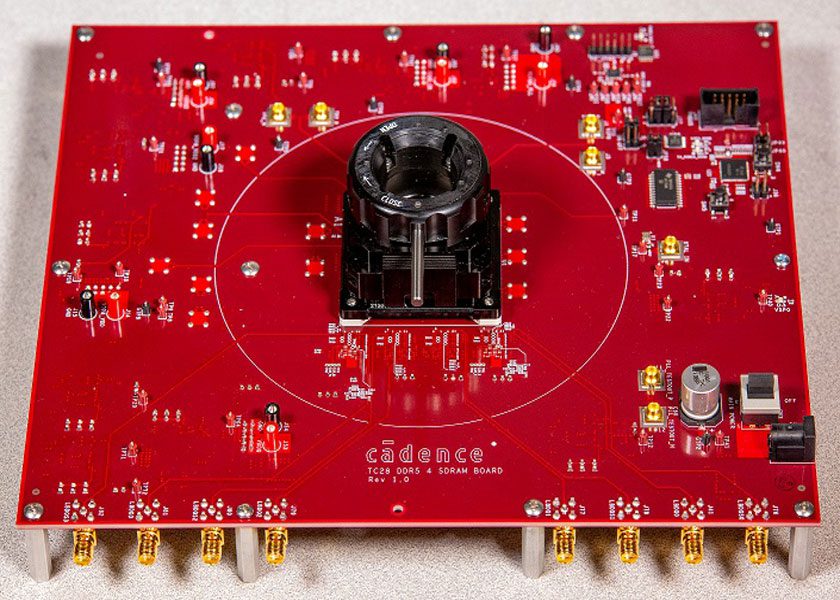

Cadence ha annunciato di aver realizzato su primo prototipo su silicio dell’IP di interfaccia per la versione preliminare dello standard JEDEC DDR5. Il chip di test Cadence è stato fabbricato con il processo da 7nm di TSMC e raggiunge una velocità di trasmissione di 4400 megatransfer al secondo (MT/s), cioè il 37,5% in più della più veloce memoria commerciale DDR4 a 3200MT/s. Grazie a questo importante risultato, i fornitori di SoC che sviluppano sottosistemi di memoria ad alta velocità per applicazioni server, storage ed enterprise di fascia alta possono iniziare a progettare i loro sottosistemi DDR5 utilizzando IP per PHY e controller testata su silicio da Cadence.

Cadence è pronta a coinvolgere immediatamente i clienti per avviare progetti SoC che integrano interfacce di memoria DDR5.

“TSMC è consapevole dell’importanza della DRAM di nuova generazione per i nostri clienti aziendali e dei data center “, ha affermato Suk Lee, direttore senior della divisione Marketing Infrastructure di Design presso TSMC. “Siamo lieti che Cadence abbia dimostrato l’interoperabilità con i prototipi di dispositivi di memoria DDR5 nel nostro processo 7nm, leader del settore. Ciò renderà possibile una maggiore larghezza di banda e densità per i futuri server e dispositivi di archiviazione prodotti da TSMC.”

“Come parte del programma di validazione e interoperabilità DDR PHY di Cadence, Micron ha fornito a Cadence prototipi di ingegneria della prima memoria per una versione preliminare dello standard DDR5“, ha dichiarato Ryan Baxter, direttore del segmento Data Center, Compute and Networking Business Unit, in Micron. “Siamo felici che il chip di prova IP DDR5 di Cadence sia in grado di interoperare in modo coerente con i nostri dispositivi di memoria alla velocità di 4400MT/sec.”

“Cadence ha compiuto un enorme passo avanti nella strada per integrare in server, storage e apparecchiature aziendali memorie ad alta velocità di nuova generazione. I sistemi che utilizzano DDR5 saranno in grado di ottenere una maggiore larghezza di banda rispetto a DDR4, utilizzando meno energia per unità di informazione trasferita, consentendo a questi sistemi di effettuare più calcoli su set di dati più grandi rispetto a quelli possibili con DDR4“, ha dichiarato Babu Mandava, vicepresidente senior e direttore generale, IP Group presso Cadence. “L’IP DDR Cadence di prossima generazione è pronto per essere implementato ora e non vediamo l’ora di attivare i progetti SoC DDR5.”

Cadence offre ai fornitori di sistemi elettronici e di semiconduttori l’opportunità di creare prodotti innovativi che trasformano il modo in cui le persone vivono, lavorano e si divertono. Software, hardware e IP per semiconduttori di Cadence sono utilizzati dai clienti per portare più rapidamente sul mercato i loro prodotti. La strategia di System Design Enablement della società aiuta i propri clienti a sviluppare prodotti innovativi – dai chip alle schede ai sistemi – rivolti alle applicazioni mobili, consumer, cloud, datacenter, aerospaziali, automotive, IoT, industriali e a molti altri segmenti di mercato.