Non ci sono prodotti a carrello.

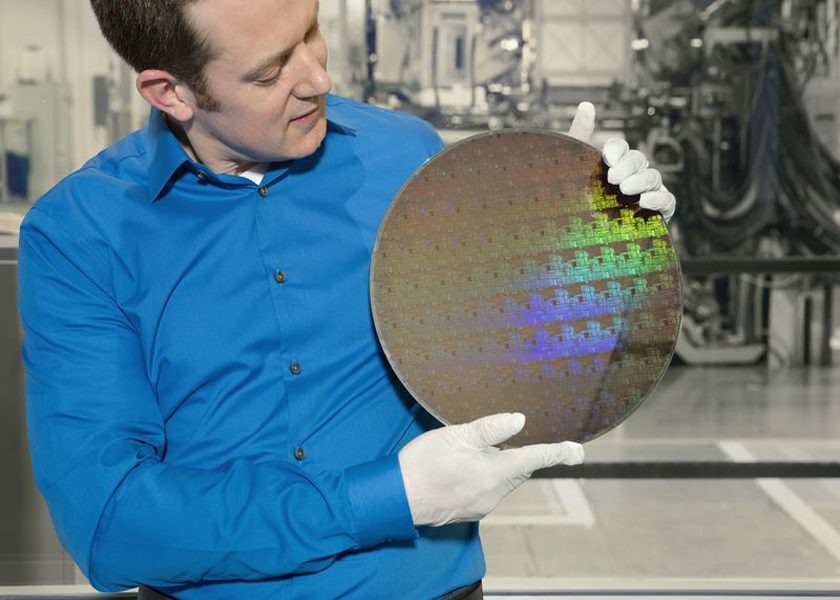

IBM ha annunciato di aver realizzare il prototipo di un transistor con tecnologia a 5 nm utilizzando il tradizionale silicio. Il processo produttivo è stato realizzato in collaborazione con Samsung e GlobalFoundries, una società che produce chip su disegno di terze parti e che vanta numerosi clienti tra cui Qualcomm e AMD.

Appena due anni fa IBM aveva annunciato di aver messo a punto un processo per la costruzione di chip a 7 nm; prodotti realizzati con questa tecnologia stanno per essere introdotti sul mercato da Samsung.

La riduzione delle dimensioni dell’elemento base di tutti i dispositivi elettronici consente di ridurre i consumi, aumentare la velocità di funzionamento e, ovviamente, di realizzare un numero maggiore di transistor a parità di superficie di silicio. Quello dei consumi è forse l’elemento più critico, anche perché i chip con 10 o 20 miliardi di transistor sono veramente pochi, processori e GPU di ultimissima generazione. Ad ogni buon conto, laddove è possibile realizzare 20 miliardi di transistor con la tecnologia 7 nm, ci possono stare 30 miliardi di elementi con la tecnologia a 5 nm. Secondo IBM la tecnologia a 5 nm può portare ad un risparmio energetico del 75 rispetto agli attuali dispositivi realizzati a 10 nm.

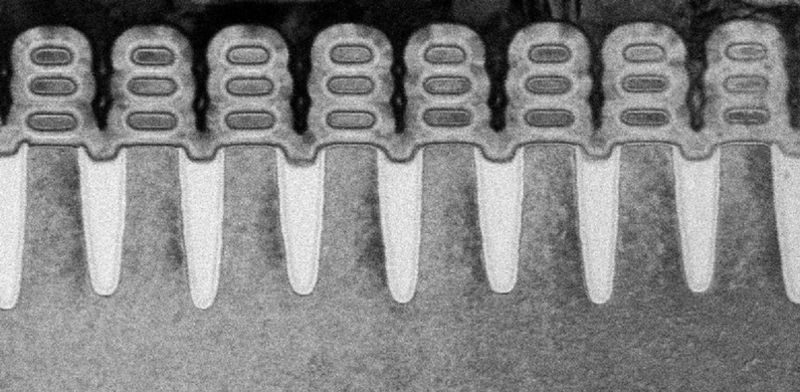

La tecnologia utilizzata da IBM per evitare fenomeni di quantum tunnelling sempre più pesanti al ridursi delle dimensioni, è quella denominata “Gate-all-around” (GAAFET), col materiale che rappresenta il gate avvolto intorno a tre sottili strati di silicio disposti in maniera orizzontale; molto diverso dalla tecnologia FinFET a disegno verticale e con il gate disposo su tre soli lati. Sotto molti punti di vista l’architettura Gate-all-around è più semplice rispetto a FinFET con possibilità di essere scalata fino a 3 nm.

Guarda il video diffuso da IBM:

Il nuovo processo, inoltre, consente una (relativamente) facile regolazione della larghezza dei nanosheets che può essere effettuata in modo continuo, tutto all’interno di un unico processo di produzione; questa regolazione consente di ottimizzare le prestazioni e la potenza di circuiti specifici, cosa che non è possibile con l’architettura FinFET.