Non ci sono prodotti a carrello.

Integra un Deep Neural Network Accelerator

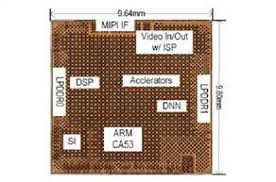

Toshiba Electronics Europe (https://toshiba.semicon-storage.com/eu/) ha annunciato lo sviluppo di un SoC (System on Chip) di riconoscimento delle immagini per applicazioni automobilistiche che implementa un acceleratore di apprendimento profondo 10 volte più veloce e 4 volte più efficiente dal punto di vista energetico rispetto al precedente prodotto Toshiba.

I dettagli della tecnologia sono stati riportati alla Conferenza internazionale ISSCC 2019 a San Francisco, il 19 febbraio.

I sistemi avanzati di assistenza alla guida, come la frenata autonoma di emergenza, offrono funzionalità sempre più avanzate e la loro implementazione richiede un SoC di riconoscimento delle immagini in grado di riconoscere con grande velocità e con un basso consumo energetico segnali stradali e situazioni stradali di pericolo.

Le reti neurali profonde (DNN), algoritmi modellati sulle reti neuronali del cervello, eseguono l’elaborazione del riconoscimento in modo molto più accurato rispetto al riconoscimento di modelli convenzionali o all’apprendimento automatico, ed è logico che trovino utilizzo anche in applicazioni automobilistiche. Tuttavia, il riconoscimento di immagini basato su DNN con processori convenzionali richiede tempo, poiché richiede un numero enorme di calcoli con accumulo multiplo (MAC). Anche il DNN ad alta velocità con processori convenzionali consuma troppa energia.

Toshiba ha superato questo problema con un acceleratore DNN che implementa l’apprendimento profondo nell’hardware e che è basato su tre caratteristiche:

- Unità MAC parallele. L’elaborazione DNN richiede molti calcoli MAC. Il nuovo dispositivo di Toshiba ha quattro processori, ciascuno con 256 unità MAC. Questo aumenta la velocità di elaborazione DNN.

- Accesso DRAM ridotto. I SoC convenzionali non hanno memoria locale per mantenere i dati temporali vicino all’unità di esecuzione DNN e consumano molta energia accedendo alla memoria locale. L’energia viene anche consumata a causa della grande quantità di dati utilizzati per i calcoli MAC. Nel nuovo dispositivo Toshiba, la SRAM è implementato vicino all’unità di esecuzione DNN e l’elaborazione DNN è suddivisa in blocchi di sub-elaborazione per mantenere i dati temporali nella SRAM, riducendo l’accesso DRAM. Inoltre, Toshiba ha aggiunto un’unità di decompressione all’acceleratore. La mole di dati, compressa e archiviata in DRAM in anticipo, viene caricata attraverso l’unità di decompressione. Ciò riduce il consumo di energia dovuto al caricamento dei dati nella DRAM.

- Accesso SRAM ridotto. Nell’apprendimento approfondito convenzionale, dopo l’elaborazione di ogni livello di DNN, c’è un accesso alla SRAM, molto oneroso dal punto di vista energetico. L’acceleratore ha una struttura di livello pipeline nell’unità di esecuzione DNN del DNN, consentendo l’esecuzione di una serie di calcoli DNN con un solo accesso SRAM.

Il nuovo SoC è conforme a ISO26262, lo standard globale per la sicurezza funzionale per applicazioni automobilistiche.

Toshiba continuerà a migliorare l’efficienza energetica e la velocità di elaborazione del SoC sviluppato e inizierà le spedizioni del campione di Visconti5, questo il nome della nuova generazione del processore di riconoscimento immagini, a settembre di quest’anno.