Non ci sono prodotti a carrello.

Le memorie HBM (High Bandwidth Memory) sono il frutto di una collaborazione tra AMD e SK Hynix nata con lo scopo di realizzare memorie con maggiore capacità di banda, minori consumi e dimensioni ridotte.

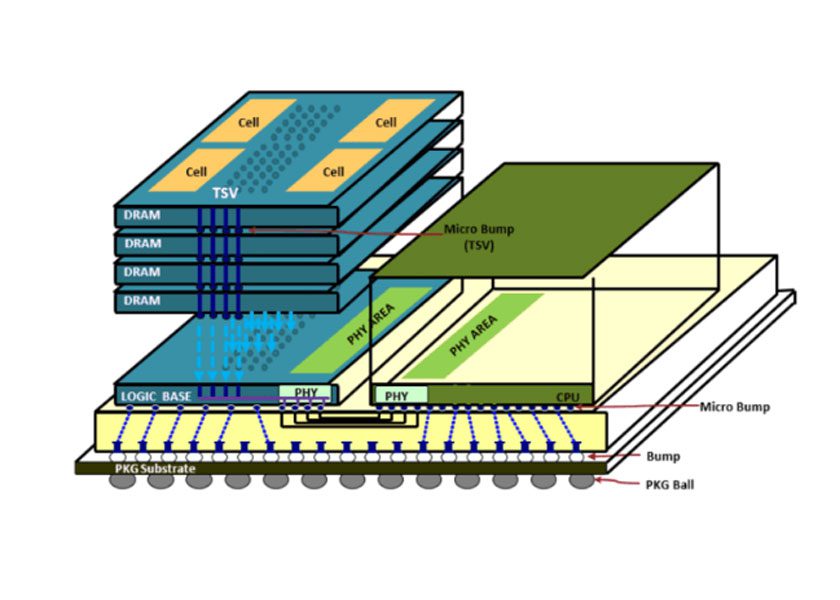

L’architettura prevede l’utilizzo di cinque die DRAM disposti verticalmente e collegati usando connessioni TSV (Through Silicon Via); ogni pila di memoria HBM comprende quattro die di archiviazione e un die logico di controllo.

Le High Bandwidth Memory sono state adottate dallo JEDEC come standard industriale nell’ottobre 2013; la seconda generazione, le HBM2, sono state codificate dallo JEDEC nel gennaio 2016.

Ogni die DRAM utilizzato della pila HBM comunica con l’esterno tramite due canali a 128 bit mentre ogni HBM dispone di un’interfaccia a 1024 bit. In questo modo la capacità di banda può superare i 100 GB/s e la frequenza i 500 MHz.

Queste memorie vengono utilizzate negli acceleratori grafici ad alte prestazione e nei dispostivi di rete. I primi dispositivi ad usare una memoria HBM sono state le GPU AMD mentre NVIDIA le utilizza nelle schede acceleratrici Tesla.

Nel 2016 è stata annunciata la terza generazione di memorie HBM il cui arrivo è previsto per il 2020, mentre le HBM+ arriveranno nel 2022 seguite dalle HBM4 nel 2024.

Le nuove versioni incrementeranno le dimensioni dello stack e offriranno maggiore bandwidth, garantendo prestazioni di storage adatte ai supercomputer exascale.