Non ci sono prodotti a carrello.

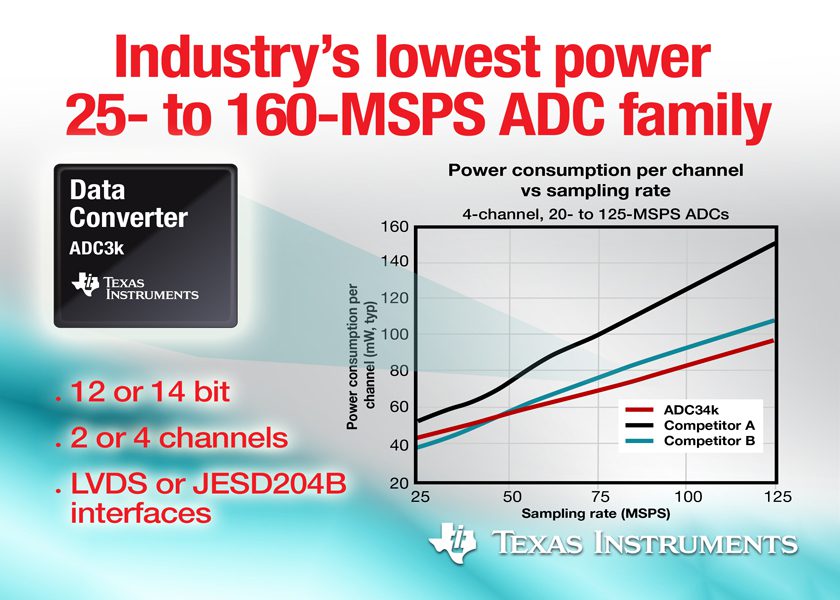

Texas Instruments ha ampliato la gamma di convertitori dati con una nuova famiglia di convertitori analogico-digitale (ADC) compatti, con compatibilità a livello di pin, che offre il miglior rapporto fra potenza e prestazioni della categoria. La famiglia ADC3k comprende versioni a 12 e 14 bit con velocità fino a 160 MSPS, con 2 o 4 canali e interfacce LVDS o JESD204B. I dispositivi sopportano l’ampia gamma di temperature da −40°C a +85°C degli ambienti industriali, per applicazioni come controllo di motori, imaging medicale, apparecchiature portatili di collaudo e misura, oltre ad applicazioni nell’ambito della difesa e delle comunicazioni, come Software Defined Radio (SDR) e MIMO (multi-ingresso e multi-uscita). Maggiori informazioni sulla serie ADC3k sono disponibili al link www.ti.com/adc3k-pr-eu

Caratteristiche e prestazioni della serie ADC3k:

- Consumi energetici e rapporto potenza/prestazioni migliori della categoria: alla massima velocità di campionamento di 160 MSPS, questi dispositivi consumano solo 200 mW/ch, 80 mW/ch in meno rispetto a dispositivi equivalenti, e offrono un rapporto potenza/prestazioni migliore del 30 %. I consumi scendono progressivamente fino a 44 mW/ch a 25 MSPS.

- Ampia gamma compatibile a livello di pin: tutti i convertitori della famiglia sono compatibili a livello di pin per offrire la piena scalabilità su diverse piattaforme e soddisfare tutte le esigenze in termini di velocità di campionamento e numero di canali.

- Dimensioni compatte per ingombri ridotti: i dispositivi da 160 MSPS a 4 canali hanno dimensioni dimezzate rispetto ai modelli attuali.

- Semplificazione dei circuiti sulla scheda: le varianti JESD204B sono conformi alle sottoclassi 0, 1 e 2 fino a 3,2 Gbps. Supportano un percorso per ogni uscita ADC fino a 160 MSPS e un percorso per due ADC fino a 80 MSPS.

- Prestazioni uniche: le funzioni opzionali di dither e chopper contribuiscono a migliorare la Spurious-Free Dynamic Range (SFDR, rapporto tra la potenza del segnale e quella della maggior componente di segnale spurio) ed eliminare il rumore l/f, consentendo ai progettisti di ottimizzare le prestazioni del dispositivo per soddisfare le esigenze del sistema.

Nuovo amplificatore per aumentare le prestazioni degli ADC3k

Il nuovo THS4541, un amplificatore rail-to-rail completamente differenziale con i consumi più bassi del settore, in grado di raggiungere un prodotto guadagno-larghezza di banda (GBW) di 850 MHz, consente ai progettisti di ottenere le massime prestazioni dai dispositivi ADC3k. Le superiori prestazioni di distorsione armonica, pari a 123/-130 dBc HD2/HD3 a 1 MHz, offrono una soluzione con accoppiamento CA o CC completamente differenziale caratterizzata da maggiore flessibilità unita a un incremento delle prestazioni del dispositivo ADC3k. La combinazione dei dispositivi offre inoltre potenza ultra-bassa e la soluzione di front-end analogico più compatta a questi livelli di prestazioni.

Strumenti e assistenza per velocizzare la progettazione

Per accelerare la progettazione di un sistema di acquisizione del segnale ad alta velocità è disponibile un progetto di riferimento TI Designs (TIDA-00294). Il progetto con interfaccia attiva ad alte prestazioni per la conversione da single-ended a differenziale comprende il convertitore ADC ADC34J22 a 12 bit, 4 canali e 50 MSPS e il THS4541. È ottimizzato per applicazioni con ingresso single-ended con accoppiamento CC, ad esempio controllo di motori, imaging medicale, apparecchiature portatili di collaudo e misura, e sistemi di difesa. Gli ingegneri possono sfruttare questa metodologia di progettazione per qualsiasi dispositivo della famiglia ADC3k.

I progettisti di sistemi possono accoppiare i moduli di valutazione (EVM) attuali o futuri per i dispositivi ADC3k JESD204B e LVDS rispettivamente con il generatore di pattern e la scheda di acquisizione dati TSW14J50EVM e TSW1405EVM per approntare un sistema di valutazione a basso costo.

Per i progettisti che utilizzano Cyclone® V SOC FPGA di Altera, Dallas Logic ha sviluppato un modulo ADC a 4 canali, 12 bit, 50 MSPS che si integra con lo standard High Speed Mezzanine Card (HSMC) di Altera. Il modulo DEV-ADC34J22 è costituito da ADC34J22 e THS4541, oltre al clock jitter cleaner LMK04828 di TI, con uscite single-ended ad accoppiamento CC su due dei quattro canali. Il modulo è commercializzato da Arrow al prezzo di 199 dollari.

La famiglia ADC3k comprenderà ben 32 dispositivi compatibili a livello di pin entro la fine del 2015, con velocità comprese fra 25 MSPS e 160 MSPS. La gamma ha un package QFN da 7×7 mm, ad eccezione delle versioni LVDS a 4 canali che utilizzano il formato QFN da 8×8 mm.